Tampereelle perustetun SoC Hubin ensimmäisen järjestelmäpiirin suunnittelu saatiin valmiiksi viime vuoden lopussa Tampereen yliopiston ja yritysten yhteistyönä. Nyt ensimmäiset fyysiset piirit on pitkälti jo testattu ja edessä ovat ensimmäiset demosovellukset.

Tamperelaisen SoC Hub -konsortion tiiviin yhteistyön ensimmäinen tulos on Ballast-nimen saanut järjestelmäpiiri, joka valmistettiin TSMC:n tehtaalla Taiwanissa. Eurooppaan saapuessaan osa piireistä koteloitiin tutkimusinstituutti Imecin toimesta ja lähetettiin sen jälkeen Tampereelle.

Järjestelmäpiirin valmistuksessa käytettiin TSMC:n uutta 22 nanometrin Ultra Low Leakage -puolijohdeteknologiaa, joka sopii erityisesti IoT- ja Edge-laitteisiin.

Ballast sisältää useita erilaisia RISC-V prosessoriytimiä, DSP- ja koneoppimiskiihdyttimet sekä laajennusrajapinnan FPGA-kiihdyttimelle. Piirille on myös toteutettu ohjelmistokehitystuki.

Testausta varten on tehty oma Graniitti-piirilevy, joka toimii jatkossa myös Ballastin kehitysalustana. Seuraavaksi testausprosessi etenee seuraavaksi alijärjestelmien yksityiskohtaisiin testeihin ja suorituskykymittauksiin.

Ballastin suunnittelu on osa Business Finlandin rahoittamaa SoC Hub -konsortioprojektia, johon kuuluvat Tampereen yliopisto, Nokia, CoreHW, VLSI Solution, Siru Innovations, TTTEch Flexibilis, Procemex, Wapice ja Cargotec.

Ballastin sovellusten ohella kehitetään jo uutta järjestelmäpiiriä, jonka suunnittelun odotetaan valmistuvan vuoden loppupuolella. Kaikkiaan tampereen SoC Hub aikoo tuottaa yhteensä kolme järjestelmäpiiriä vuoden 2023 loppuun mennessä.

Lisää: SoC Hub (LINKKI) ja aiemmat Soc Hubia käsitelleet uutiset (LINKKI).

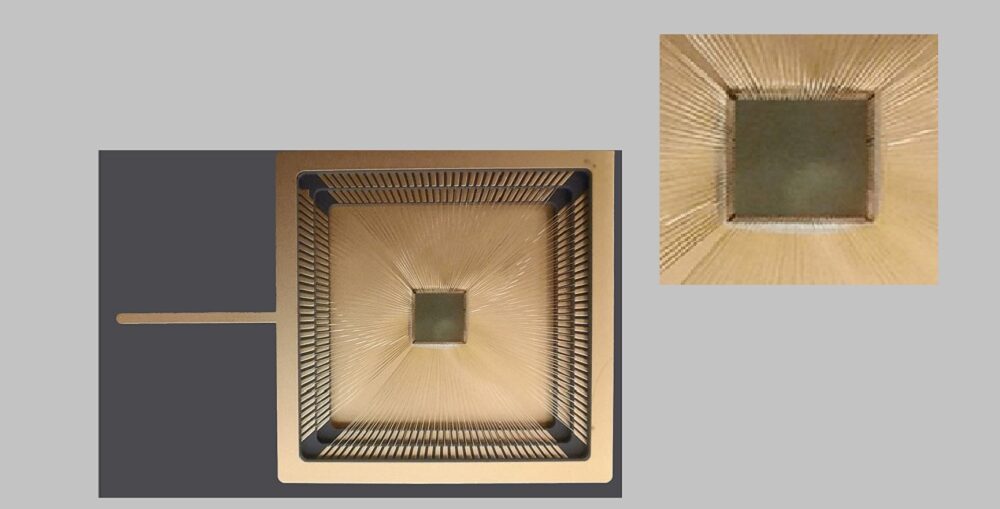

Kuva: Soc Hubin TSMC:n valmistama Ballast-piiri kytkettynä kultalangoilla piirilevylle juotettavaan koteloon. Kuva: Tampereen yliopisto