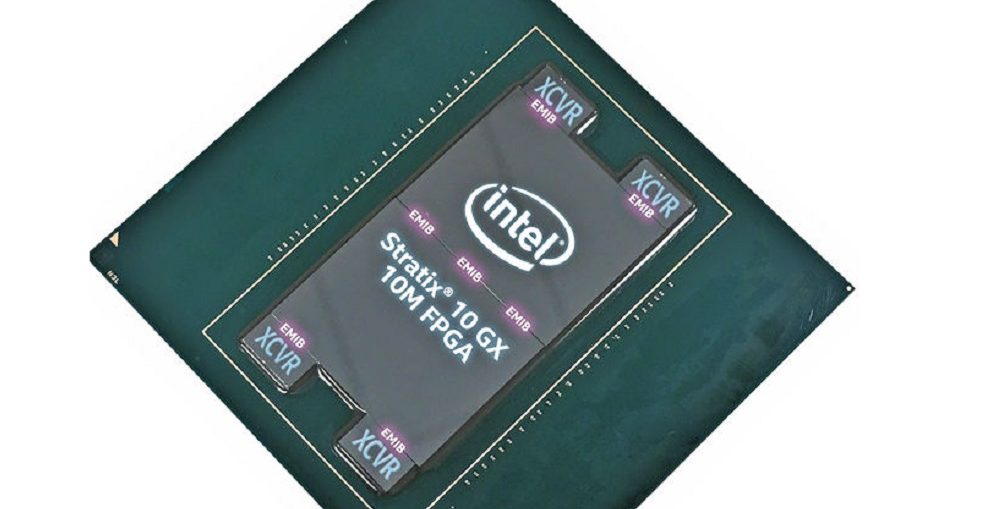

Intel on saanut tuotantoon uudet kahdesta sirusta rakentuvat Stratix 10 GX 10M FPGA -piirit. Niissä on yhteensä 10,2 miljoonaa logiikkaelementiä (LE), joka on hieman enemmän kuin yhden sirun ratkaisuna toteutetuissa Xilinxin Virtex UltraScale VU19P -piireissä.

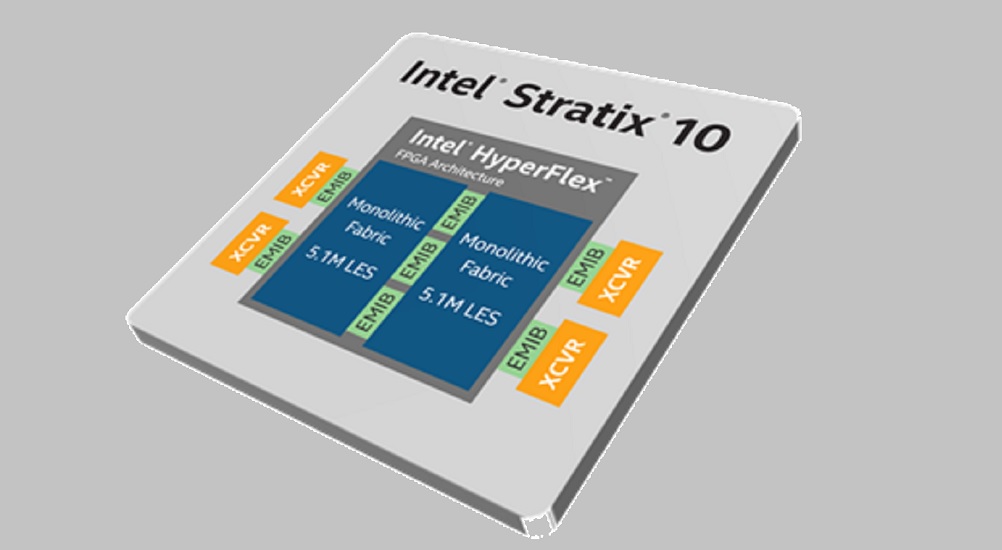

Intel uusi Stratix 10 GX 10M FPGA perustuu Stratix 10 FPGA -arkkitehtuuriin ja Intelin Embedded Multi-die Interconnect Bridge (EMIB) -liitäntätekniikkaan.

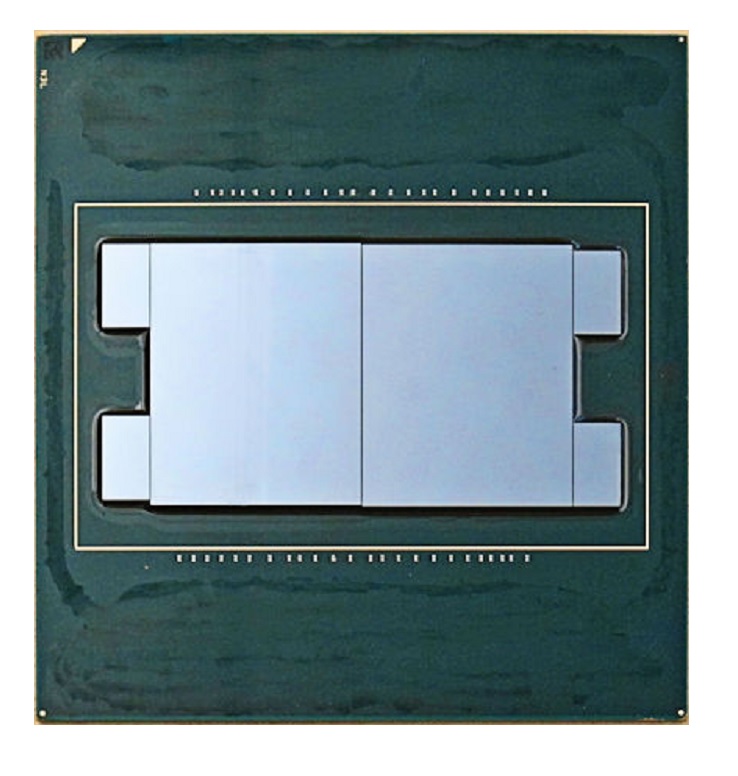

Intel on aiemmin käyttänyt EMIB-liitäntätekniikkaa kytkeäkseen SRAM-muistia yhteen FPGA-sirun kanssa. Nyt EMIB-tekniikan avulla voidaan kaksi 5,1 miljoonan loogisen elementin sisältävää piisirua yhdeksi paketiksi.

Liitäntäratkaisun avulla Intel Stratix 10 GX 10M FPGA on Intelin mukaan noin 3,7 kertaa tiheämpi kuin aikaisempi yrityksen Stratix 10 -laiteperheen tihein jäsen 10 GX 1SG280 FPGA.

Yhä suurimpien FPGA-piirien käyttö mahdollistaa isojen ASIC-, ASSP- ja SoC-mallien toteuttamisen helpommin pienemmällä määrällä FPGA-piirejä emulointilaitteistossa.

Liitäntäväylän kautta esimerkiksi Stratix 10 DX FPGA-piiri pystyy tarjoamaan myös PCIe 4.0 -yhteensopivuuden.

Lisää: Intel (LINKKI), tuotetiedot blogisssa (LINKKI) ja aiempi uutinen Xilixin Virtex UltraScale+ VU19P -FPGA-piiristä (LINKKI) ja Intelin 5G-FPGA-piiristä (LINKKI)

Kuva: Intel

Tärkeimmät teknologiauutiset kätevästi myös uutiskirjeenä! Tilaa (LINKKI)

LUE – UUTTA – LUE – UUTTA – LUE – UUTTA

Uusi ammattilehti huipputekniikan kehittäjille – Lue ilmaiseksi verkosta

https://issuu.com/uusiteknologia.fi/docs/2_2019/